# REPUBLIQUE ALGERIENNE DEMOCRATIQUE POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

# UNIVERSITE DE TISSEMSILT

FACULE DES SCIENCES ET DE LA TECHNOLOGIE

Département Sciences et technologies

# Polycopié de cours

# La technologie et fabrication des circuits intégrés

Domaine: Sciences et technologie

Filière : électronique

Spécialité : électronique

Préparé par : Dr. CHEBBAH KHEIRA.

Maitre de conférence classe « B » Année universitaire : 2022/2023.

Les étudiants concernés par le support : Troisième année licence électronique.

# Table des matières

| Chapitre I : Introduction a la microélectronique                |     |

|-----------------------------------------------------------------|-----|

| I- Introduction                                                 | 1   |

| II-Type des circuits intégrés                                   | 4   |

| II-1- Circuits intégrés analogiques                             | 4   |

| II-2- Circuits intégrés numériques                              | 4   |

| II-3- Circuits intégrés mixtes                                  | 5   |

| III- Composition                                                | 5   |

| III-1- le boitier                                               | 5   |

| III-2- Le Die                                                   | 7   |

| III-3- Notion d'intégration                                     | 8   |

| III-4- Échelle d'intégration                                    | 8   |

| III-5- Les familles des circuits intégrés                       | 9   |

| III-5-1- Les familles TTL                                       | 9   |

| III-5-2- Les familles CMOS                                      | 11  |

| III-5-3- Les familles ECL                                       | 11  |

| III-5-4- Familles hybrides                                      | 12  |

| III-6- Les critères de choix des familles et des séries         | 12  |

| Chapitre II : fabrication des substrats de silicium monocristal | lin |

| I- La fabrication des circuits intégrés                         | 13  |

| I-1- La fabrication du substrat en silicium                     | 13  |

| Chapitre III: Techniques de dopage du silicium                  |     |

| I-1 Semi-conducteurs                                            | 17  |

| I-2- La théorie de diffusion                                    | 19  |

| I-3- La diffusion de dopant                                     | 19  |

| I-4- L'implantation ionique                                     | 25  |

| I-5- Recuit thermique                                           | 27  |

| I-6- Diffusion thermique (100°C-1200°C)                         | 27  |

| Chapitre IV: l'oxydation de silicium                                          |      |

|-------------------------------------------------------------------------------|------|

| I-1 Oxydation                                                                 | 29   |

| I-1- L'oxydation thermique en présence d'oxygène, dite oxydation sèche        | 29   |

| I-2- L'oxydation thermique par voie humide en présence d'oxygène et de vapeur |      |

| d'eau                                                                         | 29   |

| Chapitre V: Les couches minces                                                |      |

| I- Les techniques de dépôt                                                    | 31   |

| I-1- Evaporation thermique                                                    |      |

| I-2- Dépôts par pulvérisation cathodique ou canon à électrons                 |      |

| I-3- Dépôts chimiques en phase vapeur à pression atmosphérique (APCVD)        |      |

| I-4- Dépôts chimique en phase vapeur assistés plasma (PECVD)                  |      |

| I-5- Dépôts chimiques en phase vapeur à basse pression (LPCVD)                |      |

| I-6- Dépôts par l'Epitaxie                                                    |      |

|                                                                               |      |

|                                                                               | ,    |

| Chapitre VI : les techniques de la Photolithographie et                       | ie . |

| gravure                                                                       |      |

| I- La photolithographie                                                       | 38   |

| I-1- Étapes principales                                                       |      |

| II- Les techniques de gravure                                                 |      |

| II-1- La gravure humide                                                       |      |

| II-2- La gravure sèche                                                        |      |

| III- Comparaison des propriétés des gravures humide et plasma                 |      |

|                                                                               |      |

| Chapitre VII : La salle blanche et la salle de montage                        |      |

| I-Introduction                                                                |      |

| I-1- Salle blanche                                                            | 45   |

|                                                                               |      |

|                                                                               |      |

| Chapitre VIII : Exemples de procédés de fabrication                           |      |

| I-1- Etape 1 : Réalisation du caisson N              | 49          |

|------------------------------------------------------|-------------|

| I-2- Etape 2 : Préparation des zones actives         | 52          |

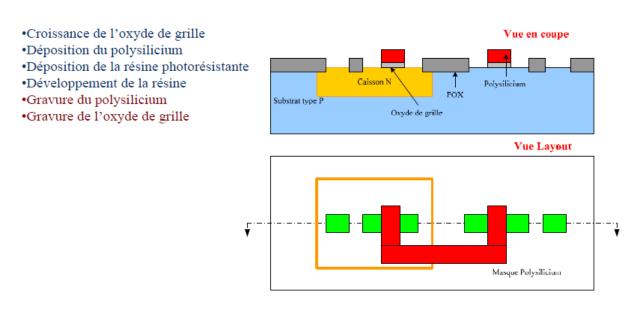

| I-3- Etape 3 : Réalisation des grilles               | 55          |

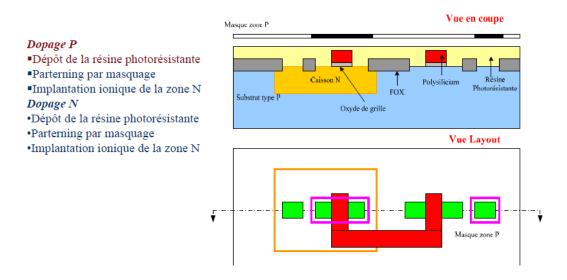

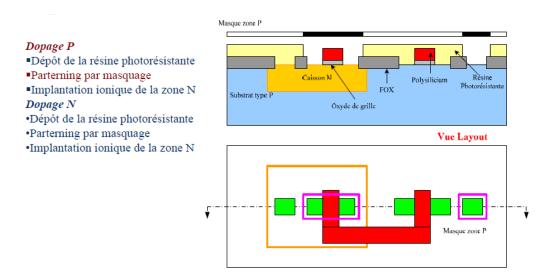

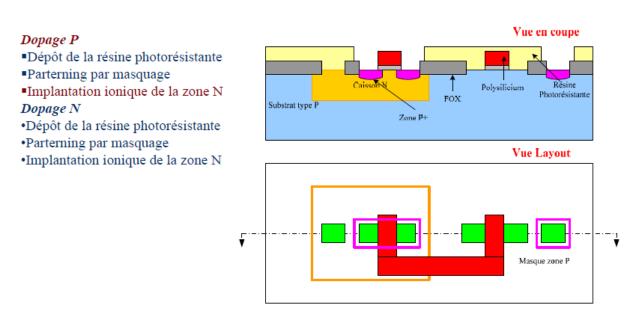

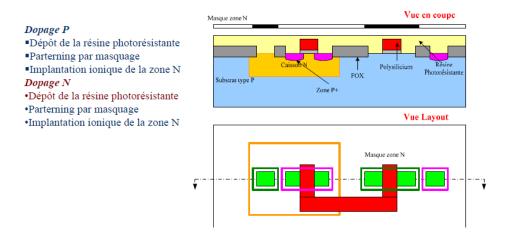

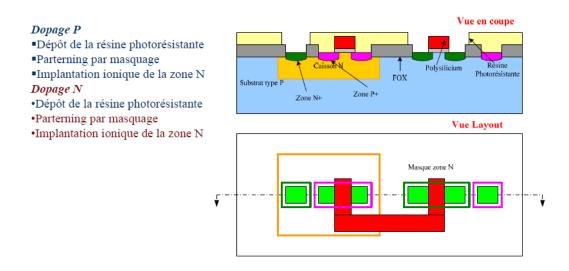

| I-4- Etape 4 : Dopage des zones actives              | 57          |

| I-5- Etape 5 : Réalisation des via de contact        | 59          |

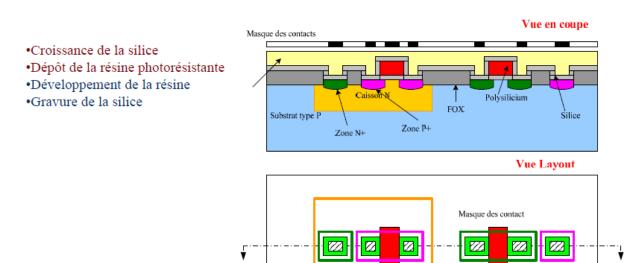

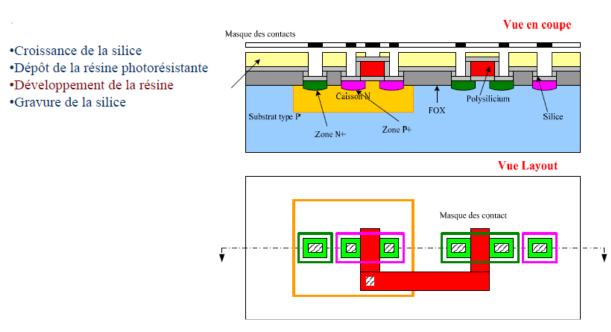

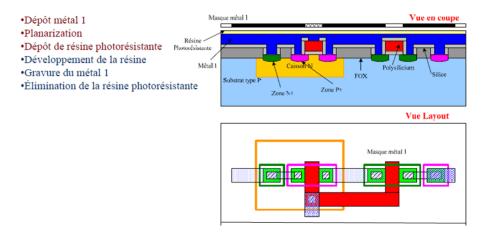

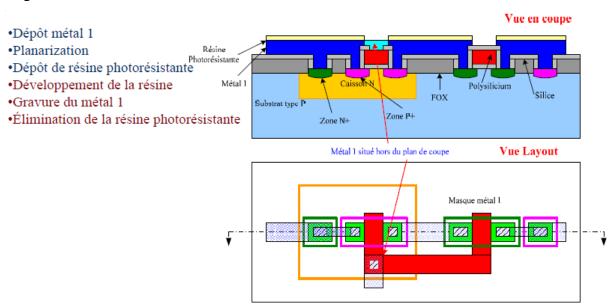

| I-6- Etape 6 : Réalisation des connexions en métal 1 | 61          |

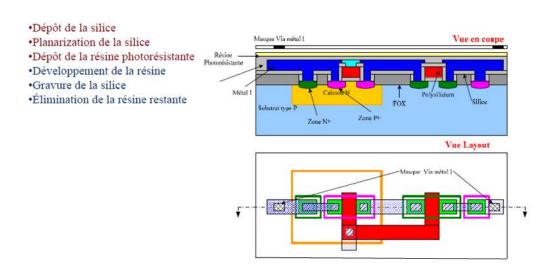

| I-7- Etape 7 : Réalisation des via métal 1 – métal 2 | 63          |

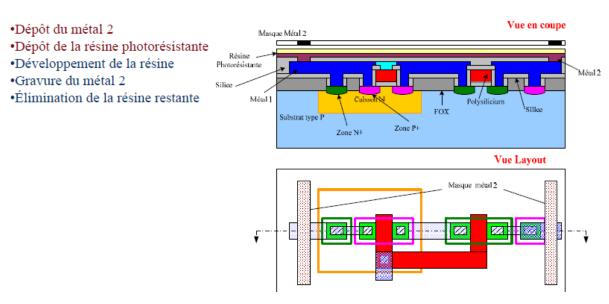

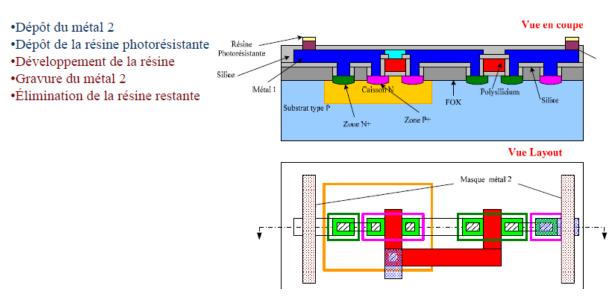

| I-8- Etape 8 : Réalisation des contacts en métal 2   | <b> 6</b> 4 |

| I-9- Finition du circuit                             | 65          |

| I-10- Le cycle complet de fabrication                | 67          |

| Référence                                            | 68          |

#### Chapitre I : Introduction a la microélectronique

#### **I- Introduction**

La microélectronique désigne l'ensemble des technologies de fabrication de composants, qui utilisent des courants électriques pour transmettre, traiter ou stocker des informations, à l'échelle micrométrique.

Elle est en grande partie à l'origine des formidables progrès réalisés ces dernières décennies dans les domaines de l'informatique, des télécommunications et de l'imagerie.

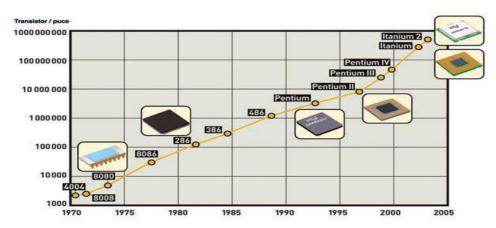

Depuis une cinquantaine d'années, l'évolution de la complexité des circuits intégrés double tous les dix-huit mois (loi de Moore). Cette évolution exponentielle a permis de réaliser, de manière monolithique, des organes électroniques de plus en plus complexes.

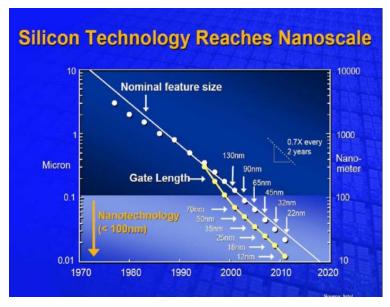

Le principal moteur de cette évolution réside dans la diminution régulière de la taille des motifs de dessin des circuits intégrés. Partis de quelques dizaines de microns dans les années 1960, ceux-ci sont maintenant inférieurs à 10 nm, et toute montre que cette évolution n'est pas terminée.

**Figure I-1**: Illustration de la loi de Moore.

Figure I-2: Evolution de la technologie silicium.

En un siècle, la miniaturisation a permis le passage du tube à vide au transistor sur matériau solide d'un micromètre carré. Parallèlement, le passage du signal analogique (à variation continue) au signal numérique (codé en une succession de 0 et de 1) a facilité le développement de circuits électroniques aux fonctions de plus en plus performantes.

La fabrication des composants microélectroniques repose sur un grand nombre de procédés qui permettent au final d'obtenir des composants élémentaires tels que les résistances, inductances, condensateurs, diodes et les transistors, ou encore les Circuits Intégrés qui ne sont en fait qu'un assemblage de ces composants élémentaires.

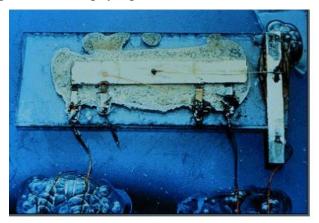

Figure I-3: Le premier transistor à pointe.

Le premier transistor à pointe a été conçu par les américains John Bardeen, William Shockley et Walter Brattain, chercheurs de la compagnie Bell Téléphone

Laboratoires, en 1947 alors qu'ils travaillaient sur les diodes RADAR. Ils ont reçu le prix Nobel de physique en 1956.

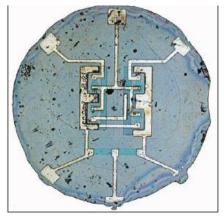

Figure I-4: Premier circuit intégré assemblé grâce au procédé planar.

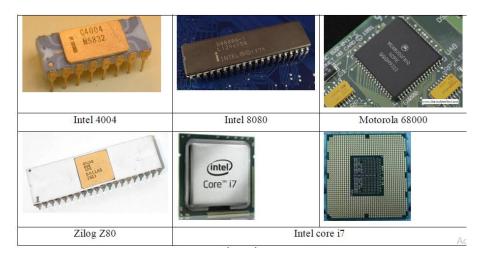

Les premiers circuits intégrés étaient réalisés en technologie bipolaire. Ils comportaient quelques dizaines de transistors. Cette technologie fut principalement utilisée pour créer les premières familles de composants logiques. En particulier, la famille TTL (pour Transistor- Transistor Logic) ou 74xx qui a perduré jusqu'à maintenant transposée en technologie MOS sous la forme de composants discrets et de cellules de circuits intégrés complexes. Vers 1970 les circuits intégrés complexes en technologie PMOS grille commencèrent à apparaître. Leur lenteur limitait leur domaine d'application à des mémoires puis aux premiers microprocesseurs. Ted Hoff conçut le premier microprocesseur commercial (Intel 4004) en 1972.

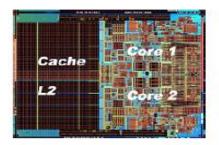

Un processeur actuel : le Conroe d'Intel avec 291 millions de transistor pour 144 mm²

Le premier processeur : l'Intel 4004 avec 2300 transistor pour 14 mm²

L'arrivée de la technologie nMOS vers 1974 permit la mise sur le marché des premiers microprocesseurs de grande diffusion 8 bits puis 16 bits (Intel 8080, 8085, 8086; Motorola 6800, 6809, 68000; Zilog Z80, Z8000; MOS 6502), et de leurs composants associés. Pour lutter contre l'augmentation de la dissipation thermique, la technologie nMOS fut remplacée par la CMOS au début des années 1980, ce qui

permit de poursuivre l'aventure jusqu'aux microprocesseurs géants actuels regroupant plusieurs centaines de millions de transistors et fonctionnant à des fréquences de plusieurs gigahertz.

**Figure I-5:** Evolution des microprocesseurs.

#### II-Type des circuits intégrés

Le composant principalement intégré est le transistor, qui constitue la base des tous types de CI. Ces circuits intègrent aussi d'autres composants : des diodes, des résistances, etc.

Il n'y a guère que les condensateurs qui sont difficiles à intégrer, bien que ce soit faisable. Un circuit intégré peut ne remplir qu'une seule fonction (c'est le cas par exemple des portes logiques), tout comme il peut remplir de nombreuses fonctions (c'est le cas par exemple du microprocesseur).

Il existe une très grande variété de ces composants divisés en deux grandes catégories : analogique et numérique.

# II-1- Circuits intégrés analogiques

Circuits qui réalisent des fonctions analogiques : amplification, modulation, filtrage, oscillateurs, etc.

Les circuits analogiques les plus simples peuvent être de simples transistors encapsulés les uns à coté des autres sans liaison entre eux, jusqu'à des assemblages complexes pouvant réunir toutes les fonctions requises pour le fonctionnement d'un appareil dont il est le seul composant.

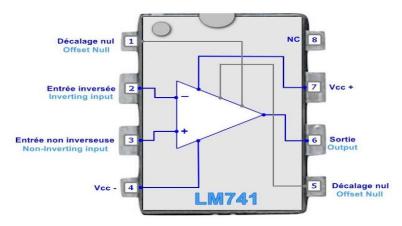

Les amplificateurs opérationnels sont des représentants de moyenne complexité de cette grande famille ou l'on retrouve aussi des composants réservés à l'électronique haute fréquence et de télécommunication.

Un exemple de circuit analogique : l'ampli op LM741 et de nombreux cousins.

#### II-2- Circuits intégrés numériques

Circuits qui réalisent des fonctions numériques : contrôle, DSP, multiplication, addition, accumulation, etc.

Un exemple de circuit numérique : inverseur 7404

Les circuits intégrés numériques les plus simples sont des portes logiques (et, ou et non), les plus complexes sont les microprocesseurs et les plus dense sont les mémoires. On trouve de nombreux circuits intégrés dédiés à des applications spécifique (ou ASIC pour Application-specific integrated circuit), notamment pour le traitement du signal (traitement d'image, compression vidéo...) on parle alors de processeur de signal numérique (ou DSP pour Digital Signal Processor). Une famille importante de circuits intégrés est celle des composants de logique programmable (FPCA, CPLD). Ces composants sont amenés à remplacer les portes logiques simples en raison de leur densité d'intégration.

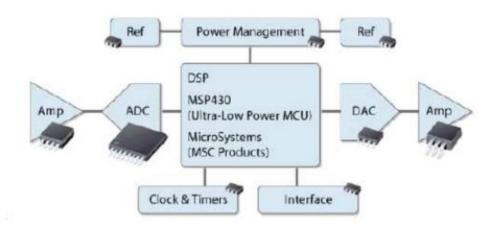

#### II-3- Circuits intégrés mixtes :

Circuits qui contiennent à la fois des fonctions analogiques et numériques sur la même puce de silicium.

Exemples : convertisseurs de données A/N ou N/A, chaine d'acquisition et de traitement de données biomédicales ou environnementales, circuits d'interfaces aux capteurs.

#### **III- Composition**

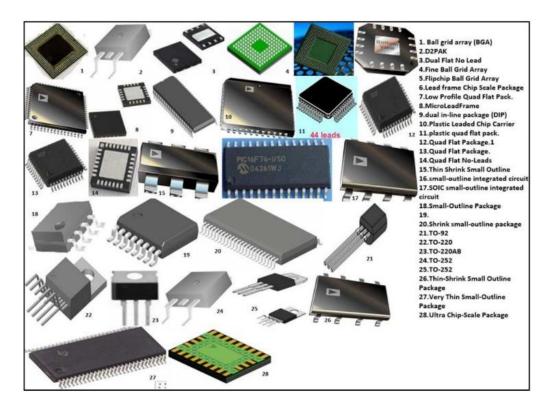

#### III-1- le boitier

Les circuits intégrés se présentent généralement sous la forme de boîtiers pleins rectangulaires, noirs, équipés sur un ou plusieurs côtés voire sur une face, de 'pattes' (appelées aussi broches ou pins) permettant d'établir les connexions électriques avec l'extérieur du boîtier. Ces composants sont brasés, (soudé, terme impropre) sur un circuit imprimé, ou enfichés, à des fins de démontage, dans des supports eux-mêmes brasés sur un circuit imprimé.

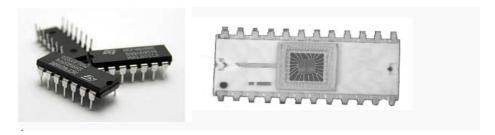

Figure I-6:: a) Circuits intégrés boîtier Dual-in-line package(DIP), b) Un Circuit intégré au centre d'un boîtier

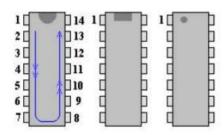

Nous remarquons aussi la présence, à l'une des extrémités du CI, une encoche. Elle est soit en forme de demi-cercle, soit en forme de rectangle, ou bien c'est un point légèrement décalé vers un des côtés.

On peut donc, à l'aide de cette encoche, trouver les numéros des pattes. En effet, la patte n°1 se situe toujours à gauche de cette encoche. Pour trouver les autres pattes, il suffit de descendre, puis de remonter sur la colonne de droite (en suivant la flèche bleue sur le dessin). Sur le boîtier peuvent être peint : le logo du fabricant, une référence qui permet d'identifier le composant, un code correspondant à des variantes ou révisions, la date de fabrication (4 chiffres codés AASS : année et semaine). Différents types de boîtiers permettent d'adapter le circuit intégré à son environnement de destination.

- Le format le plus ancien a pour nom Dual Inline Package (DIP ou DIL) qui se traduit sommairement par « boîtier avec deux lignes ».

- La miniaturisation aidant, les circuits dits de surface ont fait leur apparition : le format SO (Small outline). Bien d'autres types existent :

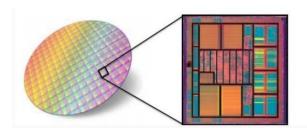

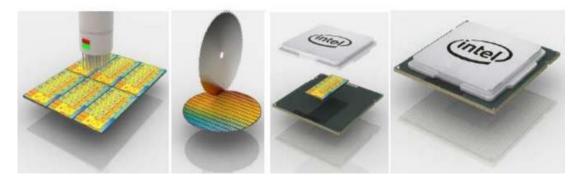

#### III-2- Le Die

Le die est la partie élémentaire, de forme rectangulaire, reproduite à l'identique (grande quantité d'éléments identiques) à l'aide d'une matrice sur une tranche de silicium en cours de fabrication. Il correspond à un circuit intégré qui sera ensuite découpé et que l'on appellera une puce avant qu'elle ne soit encapsulée (packaging) pour donner un circuit intégré complet, prêt à être monté sur une carte (**Figure I-8**).

Figure I-7 : Un die de circuit intégré VLSI

**Figure I-8 :** dies (puce individuelle) sont découpés et enfermes dans leur boitier final.

Le Die d'un circuit intégré comprend sous des formes miniaturisées principalement des transistors, des diodes, des résistances, des condensateurs, plus rarement des inductances, car elles sont plus difficilement miniaturisables.

#### III-3- Notion d'intégration

Un circuit intégré regroupe, sur un même substrat (puce, chip), l'ensemble des composants électroniques nécessaires pour réaliser une fonction donnée (logique ou analogique). Il est constitué de :

- composants actifs : transistors bipolaires (TTL, ECL) ou unipolaires (NMOS, PMOS, CMOS);

- composants passifs : diodes, résistances, condensateurs, ... ;

- connexions entre composants.

#### III-4- Échelle d'intégration

L'échelle d'intégration définit le nombre de portes logiques (ou transistors) par boîtier :

| Nom  | Signification                | Année de sortie | Nombre de<br>transistors | Nombre de portes<br>logiques par boîtier |

|------|------------------------------|-----------------|--------------------------|------------------------------------------|

| SSI  | Small Scale Integration      | 1964            | 1 à 10                   | 1 à 12                                   |

| MSI  | Medium Scale Integration     | 1968            | 10 à 500                 | 13 à 99                                  |

| LSI  | Large Scale Integration      | 1971            | 500 à 20 000             | 100 à 9 999                              |

| VLSI | Very large Scale Integration | 1980            | 20 000 à 1 000 000       | 10 000 à 99 999                          |

| ULSI | Ultra Scale Integration      | 1984            | 1 000 000 et plus        | 100 000 et plus                          |

Ces distinctions ont peu à peu perdu de leur utilité avec la croissance exponentielle du nombre de portes. Aujourd'hui plusieurs centaines de millions de transistors (plusieurs dizaines de millions de portes) représentent un chiffre normal (pour un microprocesseur ou un circuit intégré graphique haut de gamme). Afin de parvenir à de tels niveaux d'intégrations, un flot de conception complexe est utilisé.

#### a- Avantages de l'intégration

- Fabrication de circuits intégrés en grande quantité → réduction du coût ;

- Fiabilité excellente (réduction du nombre de composants discrets) ;

- Consommation de plus en plus réduite ;

- Possibilité de réaliser des circuits très complexes avec un encombrement très réduit.

#### b- Inconvénients de l'intégration

- Certains composants sont difficilement intégrables : inductances et capacités de fortes valeurs, transistors de puissance ;

- Un circuit intégré remplit une fonction bien déterminée → il ne peut pas être modifié par l'utilisateur ;

- La conception d'un nouveau circuit intégré nécessite un investissement économique important. Cependant, il existe des circuits intégrés contenant des composants électroniques non interconnectés : les connexions peuvent être réalisées à la demande de l'utilisateur → personnalisation de circuits intégrés (ASIC : Application Specific Integrated Circuits).

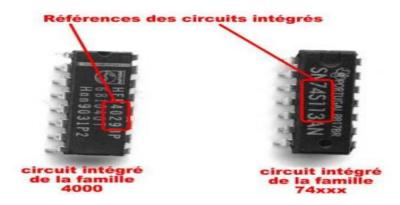

#### III-5-Les familles des circuits intégrés

Pour le concepteur de système numérique un circuit apparaît comme une « boite noire » dont le fonctionnement est entièrement défini par ses caractéristiques externes, tant statiques (volts et milliampères) que dynamiques (nanosecondes et mégahertz). Avant d'aborder ces deux points, nous passerons en revue, de façon très générale les familles les plus utilisées en pratique. Il existe deux catégories de familles de circuits logiques. Les familles qui utilisent des transistors bipolaires (TTL, ECL) et les familles qui utilisent des transistors MOS (PMOS, NMOS, CMOS).

#### III-5-1- Les familles TTL

Famille historique s'il en est, apparue au milieu des années 1960, la famille TTL (Transistor Transistor Logic), construite autour de transistors bipolaires, est devenue un standard de fait. Les premières versions sont devenues complètement obsolètes mais servent d'éléments de comparaison. Dans la version TEXAS INSTRUMENT, repris par de nombreuses secondes sources, le code d'identification d'un circuit TTL est relativement standardisé : SN 74 AS 169 N ou DM 54 S 283 J

Chaque champ a une signification:

- SN, DM : champ littéral qui indique le constructeur.

- -74 ou 54 : gamme de températures normale (0°C à 70°C) ou militaire (-55° C a  $+125^{\circ}$  C).

- AS, S, ...: technologie ici advanced shottky, shottky.

- 169, 283, ...: fonction logique.

- N, J, P, NT...: type de boîtier (ici DIL plastique ou céramique).

Un code de désignation permet d'identifier chaque

Dans l'exemple précédent il s'agit de :

SN: fabricant Texas

74 : Série grand public de 0°C à 70°C

LS: Famille TTL Low power Schottky

32 : Quadruple porte OU à deux entrées

N: Boîtier DIL 14

```

SN 74 LS 32 N

Type de Boîtier

N° du circuit (définit la fonction) jusqu'à 5 chiffres

Famille (technologie employée)

Série 74 ou 54

74: grand public de 0°C à 70°C et 54: militaire de -55°C à 125°C

Code du fabricant (SN = Texas Instruments)

```

Il existe 7 sous-familles TTL (Transistor Transistor Logique) Logique à Transistor Bipolaire:

• 74 XXX : TTL Standard

• 74L XXX : TTL Low Power (Faible consommation)

• 74S XXX : TTL Schottky (Rapides)

• 74F XXX : TTL Fast (Rapide sans Schottky)

• 74LS XXX : TTL Low Power Schottky (Faible consommation

• 47AS XXX : TTL Advanced Schottky (Encore plus rapide avec Schottky)

74ALS XXX: TTL Advanced Low Power Schottky (Faible conso+Encore plus rapide Schottky)

Les familles TTL nécessitent une alimentation monotension de +5 V à  $\pm$  5%. NB : Le dépassement de la tension d'alimentation maximum, de même que l'inversion de cette tension, par permutation accidentelle entre masse et alimentation, est l'un des moyens de destruction du circuit le plus sûr.

#### **III-5-2- Les familles CMOS**

Les CI en technologie CMOS (Complementary Metal Oxyde Semiconducteur) sont réalisés à partir de transistors MOS. Comparée à la technologie TTL cette technologie est plus lente, consomme moins d'énergie, a une marge de sensibilité aux bruits plus large, fonctionne sous une gamme de tensions d'alimentations plus grande, a une sortance plus élevée et une densité d'intégration plus importante. Néanmoins la technologie TTL est plus rapide. La série 4000, s'est rendue populaire par sa très faible consommation statique (pratiquement 0) et par une grande plage de tension d'alimentation (3 à 15 V) avec Gamme de température : de – 40 °C à + 85 °C.

En technologie MOS il existe 2 sous-familles différentes :

➤ 4XXX CMOS Classiques.

- > 74Cxx (technologie identique à la série 4000).

- On peut classer les CI MOS en trois catégories :

- NMOS : Constitué uniquement de transistors MOS à enrichissement canal N.

- PMOS : Constitué uniquement de transistors MOS à enrichissement canal P.

- CMOS : Constitué de transistors MOS à enrichissement canal N et à enrichissement canal P.

A cause de leurs différences physiques et de leur principe de fonctionnement les NMOS ont une densité d'intégration deux fois supérieure à celle des PMOS et ils sont plus rapides (les électrons se déplacent plus vite que les trous

#### III-5-3- Les familles ECL

Les familles ECL (Emitter Coupled Logic : logique à émetteurs couplés) travaillant en tout ou rien (TOR). Très rapides, temps de propagation inférieur à la nanoseconde pour une porte, temps d'accès de moins de 10 nanosecondes pour les mémoires, ces familles constituent un monde à part. Elles sont strictement incompatibles avec la TTL, ne serait-ce que par leur tension d'alimentation qui est négative, –5,2 V, et par des niveaux logiques hauts et bas de

−1 V et −1,6 V respectivement. Le fonctionnement interne fait appel à des amplificateurs différentiels, en technologie bipolaire, qui fonctionnent en régime linéaire.

Les domaines d'applications des technologies ECL sont les « super ordinateurs », et les parties hautes fréquences des systèmes de télécommunication.

#### III-5-4- Familles hybrides

Ces familles intègrent des transistors bipolaires et des transistors CMOS. Elles réunissent les qualités des deux technologies :

- Rapidité de la TTL

- Faible consommation de la CMOS

#### Exemple:

- ➤ CMOS RAPIDES 74HCxx et 74 HCTxx

- ➤ CMOS Advanced 74AC11xx et 74ACT11xx

- CMOS Low Voltage 74LVxx et 74LVCxx 6.4

#### III-6- Les critères de choix des familles et des séries

- a- Le choix dépend essentiellement de :

- La tension d'alimentation

- La tension de sorties

- La rapidité de traitement

- L'immunité au bruit électronique (tensions parasites)

- **b-** Une famille logique est caractérisée par ses paramètres électriques :

- ❖ La plage des tensions d'alimentation et la tolérance admise sur cette valeur,

- La plage des tensions associée à un niveau logique, en entrée ou en sortie,

- Les courants pour chaque niveau logique, en entrée ou en sortie,

- Le courant maximum que l'on peut extraire d'une porte logique et le courant absorbé en entrée,

- ❖ La puissance maximale consommée qui dépend souvent de la fréquence de fonctionnement.

- c- Les performances dynamiques principales sont :

- Les temps de montée (transition bas-haut) et de descente (transition haut-bas) des signaux en sortie d'une porte,

- Les temps de propagation d'un signal entre l'entrée et la sortie d'une porte logique.

# Chapitre II: fabrication des substrats de silicium monocristallin

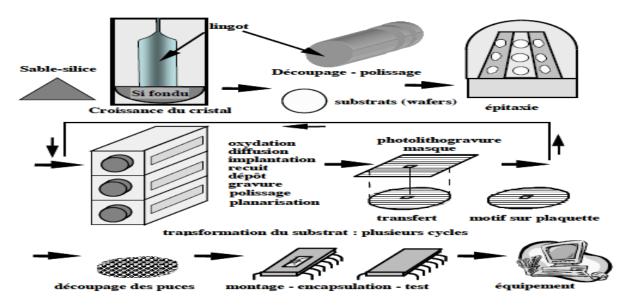

#### I- La fabrication des circuits intégrés

La fabrication des circuits intégrés répond à un nombre important de processus parfois répétés plusieurs fois.

#### I-1- La fabrication du substrat en silicium

Le silicium existe en grande quantité à la surface du globe terrestre. Les sources naturelles sont essentiellement les silicates, zircon, jade, mica et quartz. Ce sont essentiellement des formes oxydées. Il est donc nécessaire de le réduire par le carbone (à très haute température) et de le purifier afin d'obtenir un matériau dit de qualité électronique (Electronic Grade Silicon). Cette purification est importante car toute la théorie des semiconducteurs est basée sur un cristal parfait ou quasi-parfait notamment à cause du dopage qui suppose une maîtrise de la concentration d'atomes dopants de l'ordre de  $10^{14}$  cm<sup>-3</sup>.

• La première étape consiste à effectuer une électrolyse dans un four à arc à électrode de graphite. Ceci permet d'atteindre la température de fusion de la silice (1415 °C) selon la formule suivante :

$$SiC_L + SiO_2_L \rightarrow Si_L + SiO_G + CO_G$$

- On obtient alors du silicium pur à 98 %. Il faut alors effectuer une distillation à partir d'un produit, liquide à température ambiante, qui contient le silicium. De nombreux procédés ont été développés basés sur le titrachlorosilane (SiCl<sub>4</sub>), le dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>), le trichlorosilane (SiHCl<sub>3</sub>), le tétrafluorosilane (SiF<sub>4</sub>) ou le tétraiodure de silicium (SiI<sub>4</sub>).

- Nous nous attarderons sur le trichlorosilane, produit le plus utilisé dans l'industrie. Il

est obtenus par pulvérisation du silicium dans du chlorure d'hydrogène (HCl) sous

forme gazeux, suivant la réaction :

$$Si_S + 3HCl_G \rightarrow SiHCl_{3G} + H_{2G}$$

• Cette réaction avec le chlore permet une purification, il ne reste alors plus qu'à réduire avec du dihydrogène, selon la formule suivante :

$$SiHCl_{3 G} + H_{2 G} \rightarrow Si_{S} + 3HCl_{G}$$

On obtient alors des lingots de silicium (en structure polycristallin) formés à partir d'un germe sur lequel est déposé progressivement le silicium. La pureté obtenue est de l'ordre de la (ppm) ce qui reste faible par rapport au dopage.

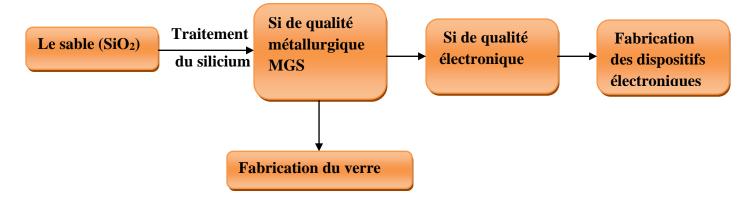

#### Les étapes de traitement du silicium

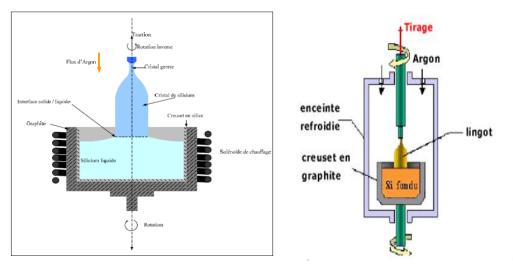

Ces lingots servent alors de charge (que l'on peut dopée ou non) à introduire dans un réacteur de croissance. La charge est alors fondue et on effectue un tirage progressif du lingot à partir d'un germe. Cette méthode de tirage est appelée "Czochralski".

**Figure II-1**: Croissance d'un lingot de silicium par la méthode de Czochralski. Le principe de la méthode Czochralski présenté croissance du cristal de la manière suivante:

- On place dans le creuset du silicium de qualité électronique que l'on chauffe jusqu'à sa température de fusion.

- Un petit cristal de silicium (le germe) est suspendu sur un support tournant. Ce germe est ensuite partiellement plongé dans le silicium en fusion.

On commence alors à retirer lentement le germe du silicium en fusion (tirage). Un refroidissement progressif permet la croissance d'un grand cristal ayant la même orientation cristalline que le germe.

Une autre technique consiste à piloter la croissance d'un germe par le déplacement d'une zone chauffée en limite de fusion du silicium (créer par une bobine parcourue par un courant de Foucault).

Le lingot obtenu est alors équeuté. Cette opération consiste à éliminer les extrémités du lingot soit mal cristallisées soit riches en impuretés.

Ces techniques ont l'inconvénient de modifier la concentration de dopant ce qui implique une variation de la résistivité le long du lingot. Une vérification des spécifications est donc nécessaire afin d'écarter les lingots de mauvaise qualité. Les lingots sont alors polis pour être parfaitement cylindrique.

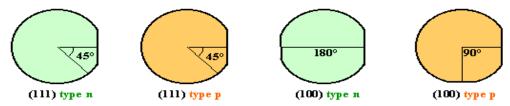

**Figure II-2 :** Lingot monocristal de Si de 300mm de diamètre et de 1m de longueur. Afin de pouvoir découper les substrats selon leurs axes cristallographiques, un repérage est effectué par la méthode de diffraction des rayons X, puis un méplat est usiné pour servir de référence.

**Figure II- 3** : Méplats d'identification des plaquettes. On peut facilement repérer les types n des types p et leurs orientations

Ils sont ensuite découpés à l'aide d'une scie diamantée ou d'un fil. Dans le cas d'une coupe par fil, les pertes sont plus faibles. Ces pertes atteignent tout de même 50% à 60% du lingot initial. On obtient alors des plaquettes ou wafers en anglais.

Afin de relaxer le cristal suite aux contraintes mécaniques imposées par le sciage et de rééquilibrer la résistivité, le lingot est recuit à 600°C.

Les plaquettes sont alors arrondies, triées en fonction de leurs épaisseurs, polis et nettoyées. Les impuretés sont éliminées par des solutions acide, puis basique et enfin l'oxyde natif est enlevé par de l'acide fluorhydrique. On réalise aussi un bombardement laser pour utiliser l'effet "getter". Les plaquettes sont triées une nouvelle fois, polies pour atteindre un effet "miroir", puis marquées au laser pour permettre un suivi lors de la fabrication. Les plaquettes sont alors vérifiées par un homme, qui reste le meilleur inspecteur.

Figure II-4: Tranches de silicium.

### Chapitre III: Techniques de dopage du silicium

#### **I-1-Semi-conducteurs**

Les semi-conducteurs sont des matériaux qui se situent entre les métaux et les isolants dans le tableau de Mendeleïev. Ils sont caractérisés par le fait que leur couche électronique superficielle contient quatre électrons (ils sont de valence 4). Les principaux semi-conducteurs sont le germanium et le silicium.

Le silicium est le principal constituant du sable. Il fut isolé en 1823 par Jöns Jacal Berzelius. Sa densité est de 2,33, son point de fusion de 1410 °C. Comme le diamant, le silicium cristallise suivant un réseau cubique. Un cristal de silicium contient 5.10<sup>22</sup> atomes au cm<sup>3</sup>.

#### a. Semi-conducteur pur ou intrinsèque

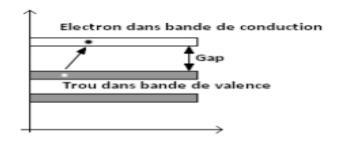

A 0 K, le semi-conducteur est isolant et la bande de conduction vide. Les électrons sont dans l'incapacité de se déplacer dans le cristal. Si l'on élève la température, l'énergie thermique va alors briser quelques liaisons covalentes et permettre à des électrons de valence d'acquérir l'énergie nécessaire pour passer dans la bande de conduction.

A noter: La différence entre les isolants classiques et les semi-conducteurs est la largeur de gap.

Plus la température est élevée, plus le nombre d'électrons de valence injectés dans la bande de conduction est grand ainsi que le courant. A 25°C, le courant étant trop faible pour être d'une quelconque utilité, un morceau de silicium n'est ni un bon isolant, ni un bon conducteur : c'est un semi-conducteur.

Représentation du déplacement d'un électron dans la bande de conduction L'électron qui a migré de la bande de valence vers la bande de conduction a laissé dans celle-ci un trou. La bande de valence n'est donc plus saturé et chaque trou correspond à une orbite disponible. Un trou est crée lors du mouvement d'un électron venu combler ce vide. Cela donne une impression de déplacement des trous dans la bande de valence.

**Figure III-1 :** Représentation du déplacement d'un électron dans la bande de conduction.

#### b. Semi-conducteurs dopés

Sachons qu'un semi-conducteur pur est un quasi isolant alors qu'un semiconducteur dopé voit sa conductibilité augmenter (au dépend de sa résistivité) et se situer entre celle d'un isolant et d'un conducteur classique.

Le dopage consiste à ajouter des atomes d'impuretés à un cristal afin d'augmenter le nombre d'électrons libres ou le nombre de trous qui sont les porteurs de charge Contribuant à la conduction.

C'est grâce à ce dopage que l'on peut créer des matériaux de type N (pour négatif) ou P (pour positif).

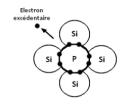

#### • Matériau de type N

Pour obtenir un matériau de type N, on incorpore dans le semi-conducteur des impuretés pentavalentes, c'est-à-dire des atomes possédant 5 électrons périphériques comme le phosphore (P) par exemple.

La couche de valence ne peut avoir plus de huit électrons. Un électron est alors excédentaire et circule sur une orbite de la bande de conduction.

Un matériau de type N, dopé avec des atomes donneurs, présente des électrons libres et des charges positives fixes égales à la quantité d'électrons libres.

Les électrons sont les porteurs majoritaires et les trous les porteurs minoritaires.

Représentation d'un cristal dopé N

#### • Matériau de type P

Lorsque la température augmente, il y génération de paires électrons-trous qui s'ajoutent aux porteurs précédents.

La majorité des porteurs sont des trous (positifs).

le semi-conducteur dopé par atome trivalent est appelé semiconducteurs de type P. Les trous sont les porteurs majoritaires.

Les électrons sont les porteurs minoritaires

#### Représentation d'un cristal dopé P

#### I-2- La théorie de diffusion

Le phénomène de diffusion est un phénomène très général dans la nature, qui correspond à la tendance à l'étalement d'espèces, particules, atomes ou molécules grâce à une excitation énergétique apportée par la chaleur. Suivant le milieu dans lequel se déplacent ces espèces, l'étalement sera plus ou moins grand.

A température ambiante le phénomène de diffusion sera très important dans un milieu gazeux, plus faible dans un milieu liquide et pratiquement nul dans un milieu solide. Pour obtenir un phénomène de diffusion dans un solide ou un cristal, il faudra chauffer le matériau à des températures voisines de 1000°C.

Dans la suite, nous nous intéresserons essentiellement aux mécanismes de diffusion dans le milieu solide, sachant qu'il est possible d'utiliser aussi des mécanismes en milieu gazeux voire liquide au niveau des mises en œuvre technologiques de procédés particuliers.

Pour mieux comprendre l'aspect macroscopique du phénomène de diffusion, il faut avoir une idée des phénomènes et mécanismes mis en jeu à l'échelle atomique.

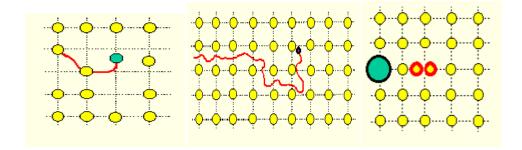

**Figure III-2 :** Mécanismes de diffusion à l'échelle atomique. Ces mécanismes seront différents suivant la nature de l'espèce diffusante et du cristal.

#### I-3- La diffusion de dopant

La diffusion consiste à faire migrer des espèces chimiques dans un milieu. Il y a trois procédés de diffusion de dopant suivant le type de source et de dopant utilisés : sources gazeuses, liquides ou solides.

#### 1) la diffusion de dopant dans le solide :

La diffusion des atomes d'impuretés introduits dans le réseau cristallin du silicium se fait par les trois mécanismes suivant

- Diffusion interstitielle

- Diffusion substitutionnelle

- Diffusion par inter change

#### a. Diffusion interstitielle:

Les atomes des impuretés se déplacent a travers le cristal en sortant d'un site interstitiel à un autre adjacent.

Dans la maile primitive de la structure Diamant il existe 5 intersites.

#### b. Diffusion par substitution:

Les atomes qui se déplacent en sautant d'un site du réseau à un autre adjacent vocaux.

Les vacances des sites sont dues essentiellement à la fluctuation thermique.

#### c. Diffusion par interchange:

C'est la Diffusion d'atome par un processus d'échange la probabilité de diffusion par inter change est très faible.

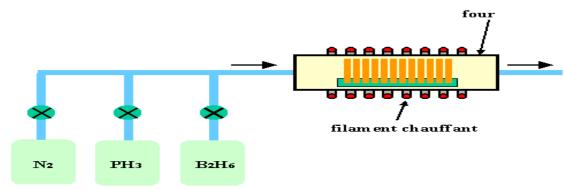

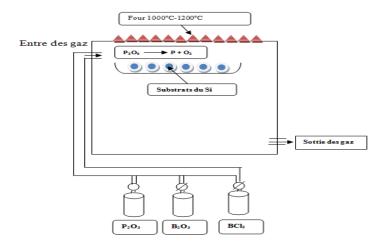

2) la diffusion de dopant dans Les sources gazeuses font appel à de l'AsH<sub>3</sub> (Arsine), la PH<sub>3</sub> (Phosphine) ou le B<sub>2</sub>H<sub>6</sub> (Diborane). Notons qu'il circule en permanence un

gaz neutre (azote) afin d'éviter toute pollution par des éléments venant de l'atmosphère ambiante. Cet azote doit être très pur afin de ne pas polluer le four. Ces gaz étant très fortement dangereux pour l'homme, on utilise plutôt la méthode liquide.

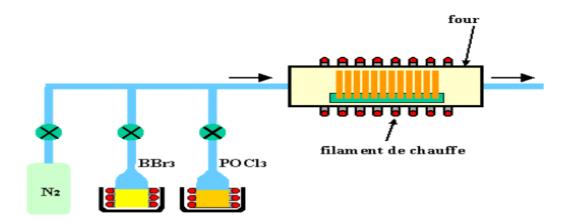

**Figure III-3 :** Diffusion dans un four à partir de sources gazeuses. Les gaz dopants sont entraînés par un gaz porteur neutre, tel que l'azote.

3) la diffusion de dopant dans Les sources liquides, on utilise principalement les sources liquides telles que le POCl<sub>3</sub> (Phosphoroxidchloride) ou le BBr<sub>3</sub> (Boron bromide). Ce sont des liquides facilement vaporisable, qui sont ensuite utilisés dans le four de diffusion sous forme gazeuse.

Figure III-4: Four de diffusion de dopants liquides

#### **Equations de diffusion**

La première loi de Fick traduit la tendance à l'étalement ; le flux d'atomes est proportionnel au gradient de concentration de ces atomes et s'exprime par :

$J = \frac{\Delta n}{\Delta t.S}$  et J: le nombre d'atome traversant par unité de surface et de temps

$$C_{1,2} = \frac{n_1 n_2}{\frac{d}{\sqrt{3}}} = \sqrt{3} \frac{n_1 n_2}{d}$$

, avec  $\frac{d}{\sqrt{3}}$ : la distance entre les plans  $(P_1, P_2)$

Après la dérivation partielle

$$\mathbf{J} = -\mathbf{D} \frac{\partial C(x,t)}{\partial x}$$

avec  $\mathbf{D} = \mathbf{D}_0 e^{\frac{E_a}{KT}} [\mathbf{cm}^2/\mathbf{s}]$

Équation dans laquelle D est le coefficient de diffusion. D dépend fortement de la température ; quasi-nul à la température ambiante, ce coefficient est de l'ordre de l'unité en micron carré par heure pour des températures de l'ordre de 1100°C.

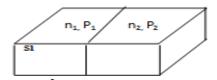

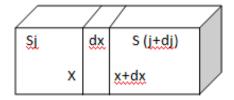

La deuxième loi à prendre en compte est l'équation de continuité. Dans un élément de volume donné, d'épaisseur dx, si le flux entrant est supérieur au flux sortant, la concentration de l'espèce considérée augmente. Cette équation est aussi utilisée pour les porteurs électrons et trous dans un semi-conducteur mais dans le cas des atomes il n'y a ni génération, ni recombinaison.

$$\frac{\partial c}{\partial t}$$

\*Sdx= Sj -S (j+dj) = -Sdj  $\rightarrow \frac{\partial c}{\partial t}$  \* dx= -dj......1

**J**: la densité des atomes traversant le P<sub>1</sub> et P<sub>2</sub>

On a:

$$\mathbf{dj} = \frac{dj}{dx} * \mathbf{dx} \dots 2$$

En replacent l'équation 2 dans l'équation 1:

$$\frac{\partial C}{\partial t}$$

\*  $dx = -\frac{dj}{dx}$ \*  $dx \rightarrow \frac{\partial C}{\partial t} = -\frac{dj}{dx}$

En appliquant le 1<sup>ere</sup> loi de Fick

$$\frac{\partial C}{\partial t} = -\frac{d}{dx}(-D\frac{\partial C}{\partial x}) \implies \frac{\partial C(x,t)}{\partial t} = D\frac{d^2C(x,t)}{dx^2}$$

la deuxième loi de Fick

Pour intégrer cette équation différentielle qui comporte une dérivation par rapport au temps et une double dérivation par rapport à l'espace, il faut déterminer 3 conditions particulières (ou limites). Ces conditions vont dépendre du procédé technologique mis en œuvre.

La résolution de la 2<sup>eme</sup> loi de Fick nous donne la distribution de la concentration

#### **Application des lois de Fick:**

Dans le phénomène de diffusion seule la région voisine à la surface sera affectée par la diffusion.

On dit que la couche se comporte comme un milieu semi infini dans la direction de la diffusion.

Condition aux limites : à t=0, C(x, 0) = 0

$C(0, t) = C_s$ : concentration de surface C=0 à t=0

$$C(x, \infty) = 0$$

#### La résolution de la 2eme loi de Fick :

L'intégration de l'équation différentielle donne :

$$C(x, t) = C_s (1-erf \frac{x}{\sqrt{4Dt}}), C(x, t) = C_s .erfc \left(\frac{x}{2\sqrt{Dt}}\right), \sqrt{Dt}$$

: longueur de diffusion,

**X**:distance (cm)

Cs: concentration superficielle (at/cm<sup>3</sup>)

erf: fonction d'erreur définit par :

$$\operatorname{erf}(y) = \frac{2}{\sqrt{\pi}} \int_0^y e^{-z^2} dz$$

$$\operatorname{erf}(0) = 0$$

,  $\operatorname{erf}(\infty) = 1$ ,  $\operatorname{erf}(-y) = -\operatorname{erf}(y)$ ,  $\operatorname{erfc}(y) = 1 - \operatorname{erf}(y)$ .

Le nombre total d'atomes d'impureté par unité de surface :

$$Q(t) = \int_0^\infty C(x, t) dx \rightarrow Q(t) = \frac{2}{\sqrt{\pi}} \cdot \sqrt{Dt} \cdot C_s \quad (at/cm^{-2})$$

Si le substrat est dopé n et les atomes sont de type p (une jonction PN) se forme la distribution devient :  $C(x, t) = [C_s \cdot erfc \cdot (\frac{x}{2\sqrt{Dt}}) - C_B]$

**C**<sub>B</sub>: concentration de bulk (substrat)

La profondeur de fonction X<sub>J</sub> peut être obtenue

à C

$$(x_j, t) = C (\infty, t) = 0$$

$\Rightarrow$   $X_j = 2\sqrt{Dt}.erfc^{-1}(\frac{x}{2\sqrt{Dt}}).\frac{C_B}{C_S}$

$X_j$ : est un paramètre très important dans les dispositifs

#### **Diffusion a source limite (Redistribution):**

Après la prédisposition, la concentration est maximale à la surface  $> 10^{22} \, \text{cm}^{-3}$  (conc)

Le but est réduire la concentration a la surface en même temps diffusé les impuretés a l'intérieur,

Ce problème est à causé de prédisposition, en pratique on dépose un oxyde de Si mince qui impureté les atomes diffuser a la surface

Les conditions aux limites :

$$\frac{\partial C(x,t)}{\partial x}\Big|_{0,t} = 0$$

à  $C(\infty,t) = 0$

La solution gaussien de l'équation de Fick est donnée par :

$$C(x, t) = \frac{Q}{\sqrt{\pi D t}} \exp \frac{-x^2}{4Dt}$$

redistribution diffusion de type gaussien

La concentration en surface varie en fonction du temps pratiquement la quantité de matière nécessaire pour une diffusion gaussienne est très faibles dans le cas du Si on possède en premier lieu a une diffusion à source constantes basse température (900°C) pendant du temps très courts la quantité de matière transportée durant la phase de dépôt est :

$$Q(t){=}2C_0 \ \sqrt{\frac{\textit{D}_1\textit{t}_1}{\pi}}$$

C<sub>0</sub>: Concentration en surface durant la phase de dépôt.

D<sub>1</sub>: Coefficient de diffusion à la température de dépôt.

t<sub>1</sub>: temps de dépôt

Ensuite la source extérieure étant levée. On place le substrat dans un four à diffusion à haut température (1200°C)

La concentration en impureté finale sera :

$$C(x,t_1,t_2) = \frac{2C_0}{\pi} \cdot (\frac{D_1t_1}{D_2t_2})^{\frac{1}{2}} \cdot \exp(\frac{-x}{2\sqrt{D_2t_2}})^2, \quad D_1t_1 \ll D_2t_2$$

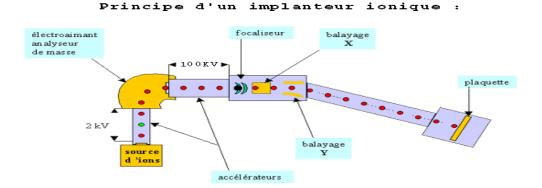

#### I-4- L'implantation ionique

Cette opération consiste à bombarder des ions sur la surface d'une plaquette afin de doper des zones précise en cours de fabrication (création de zones de source ou de drain d'un transistor MOS, d'une base et d'un émetteur dans un transistor bipolaire...). Généralement, la profondeur d'implantation varie de 100 Å à 1 mm.

Cette technique offre un contrôle précis des concentrations de dopant dans le substrat (mesurées en nombre d'atomes par unité de surface), mais elle créée des dommages dans la structure cristalline qui impose un recuit thermique.

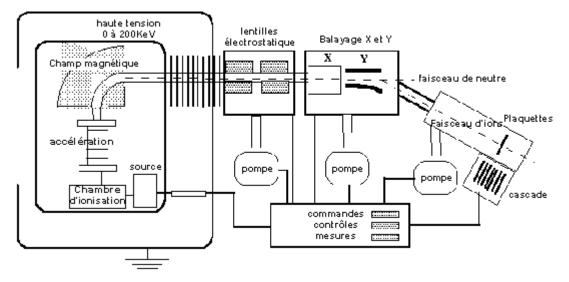

L'implanteur est en pratique un accélérateur d'ions. Il est composé des parties suivantes visibles sur la figure III-5 :

- génération des ions à partir d'une source solide, liquide ou gazeuse dans un plasma excité à 25kV,

- sélection des ions par champ magnétique effectuant le tri par le rapport masse sur charge,

- accélération des ions à l'énergie d'implantation souhaitée,

- mise en forme du faisceau d'ions par des lentilles électrostatiques,

- dispositif de balayage en x et y afin d'implanter de façon uniforme les plaquettes. Les fréquences de balayage sont telles qu'il y ait en permanence glissement de la courbe de Lissajous associée.

Figure III-5: Un implanteur ionique.

#### Avantage de l'implantation :

- la distribution en profondeur des impuretés dans un échantillon est facilement contrôlé par l'énergie du faisceau d'ion ( pas facile en diffusion)

- la quantité totale introduite peut être facilement mesuré par le courant.

- la précession est meilleure.

- L'implantation est réalisée la température plus basse que la diffusion.

- Le profil d'implantation peut être contrôlé de façon précise.

#### La distribution des ions après implantation :

La concentration N(x) des ions implantes en jet de la profondeur est donnée une distribution gaussienne

$$\mathbf{N}(\mathbf{x}) = \mathbf{N}_{\max} \exp \left( \frac{x - R_p}{2\Delta R_p^2} \right)$$

$N_{max}$ : concentration maximal a  $R_{p.}$

$2\Delta R_p$ : déviation standard.

Rp : par cour projeté en Cm avec  $N_{\text{max}} = 3. \ 10^{14} \text{ L.t} \frac{I.t}{A \Delta R_p}$

I : courant du faisceau d'ion.

T: temps d'implantation

A : surface du faisceau la cible

#### I-5- Recuit thermique

Le recuit du matériau (substrat) implanté à un double but

- Ramener la concentration de défaut à une concentration aussi faible.

- Obliger les impuretés à passer à des sites ou ils sont électriquement active

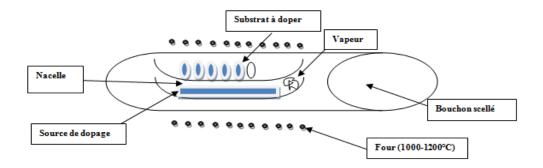

#### I-6- Diffusion thermique (100°C-1200°C)

La technique de diffusion thermique pratiquement il excite trois techniques de diffusions

- 1- la diffusion en tube scelle

- 2- la diffusion en tube ouvert

- 3- la diffusion en tube à partir d'un film

#### 1- la diffusion en tube scelle :

On connaissant le volume d'ampoule, la caractéristique du dopant, la surface globale du s/c, pression initial, température.

On peut déterminer le profil de diffusion dans le s/c.

#### 2- la diffusion en tube ouvert

Dans le tube circule un flux de gaz propre (argon, azote, hydrogène,  $O_2$ ) + les gaz dopant.

#### 3- la diffusion à partir d'un film

#### Chapitre IV: l'oxydation de silicium

#### **I- Oxydation**

L'oxydation est une étape très importante dans la fabrication des C I. L'oxydation consiste à créer une couche d'oxyde (SiO<sub>2</sub>) sur le substrat de silicium afin de s'en servir :

- de masque d'implantation ou de diffusion de dopants.

- de couche passivant à la surface du silicium.

- de zones d'isolation entre différents composants.

- de couche active dans les transistors MOS (oxyde de grille).

- d'isolation électrique entre des couches proches.

- d'isolation électrique entre les différents niveaux de métallisation ou de couches conductrices.

- de couches sacrificielles.

Il existe plusieurs techniques pour obtenir un oxyde dans un four similaire à celui de diffusion :

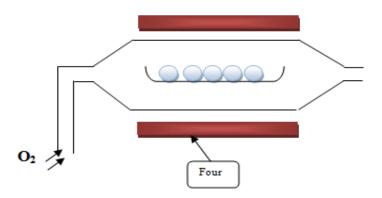

# I-1- L'oxydation thermique en présence d'oxygène, dite oxydation sèche :

C'est la plus lente, on obtient donc peu de défauts électriquement natif.

#### **Dispositif:**

# I-2- L'oxydation thermique par voie humide en présence d'oxygène et de vapeur d'eau

$Si_{solide} + 2H_2O \rightarrow SiO_{2 solide} + 2H_2$

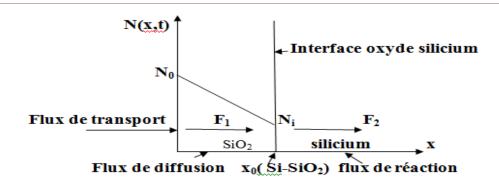

N(x,t): concentration d'oxyde a la surface

$\mathbf{F_1} = \mathbf{K_s} \, \mathbf{N_i}$  avec  $\mathbf{Ks}$ : coefficient de réaction.

A=1000°C,  $N_0$ =5.10<sup>16</sup> Molécules/cm<sup>3</sup>  $\rightarrow$  oxydation sèche.

$A=1000^{\circ}C$ ,  $N_0=3.10^{19}$  Molécules/cm<sup>3</sup>  $\rightarrow$  oxydation en phase vapeur (oxydation humide).

On peut déterminer alors le taux de croissance de l'oxyde en considérant les flux d'oxydant dans l'oxyde et à l'interface oxyde – silicium.

#### La 1ère loi de fick:

$$\mathbf{F} = -\mathbf{D} \, \frac{dN}{dx}$$

Le flux a travers l'oxyde et donner par les espaces oxydant

$$\mathbf{F}_1 = \frac{D(N-N_i)}{x_0} \quad \dots \dots (1)$$

$N_i$ : concentration des oxydants à l'interface x=x0

**D**: coefficient de diffusion

X<sub>0</sub>: épaisseur de l'oxyde

$\triangleright$  Le flux à l'interface oxyde-Silicium est déterminé par la constante de réaction à l'interface  $K_s$  donné par  $F_2 = K_s N_i \dots (2)$

A l'équilibre :  $F = F_1 = F_2$

à partir les relation (1) et (2) on a :

$$N_i = \frac{N_0}{1 + K_s \frac{x_0}{D}}$$

et  $F = \frac{N_0}{\frac{1}{K_s} + \frac{x_0}{D}}$

#### La croissance d'oxyde SiO2:

Est déterminer par le flux et le nombre de molécule  $N_1$  nécessaire pour former un volume unitaire de l'oxyde.

Dans l'oxyde de Silicium SiO<sub>2</sub> on a 2,2.10<sup>22</sup> molécules/cm<sup>3</sup>

Nous avons besoin de 2,2.10<sup>22</sup> molécules/cm<sup>3</sup> de O<sub>2</sub> (sèche)

Nous avons besoin de 4,4.10<sup>22</sup> molécules/cm<sup>3</sup> de 2H<sub>2</sub>O

L'équation de taux de croissance de l'oxyde de silicium

$$\frac{dx_0}{dt} = \frac{F}{N_1} = \frac{\frac{N_0}{N_1}}{\frac{1}{K_S} + \frac{x_0}{D}} \quad .....(3)$$

En intégrant (1) entre 0 et t

$$\mathbf{x}_0$$

-  $\mathbf{x}_i \frac{K_s}{2D} (x_0^2 - x_i^2) = \frac{N_0 K_s t}{N_1} \dots (4)$

$x_i$ : oxyde initial à t=0

En resaluant l'équation (4):

$$x_0 = \frac{A}{2} (\sqrt{1 + \frac{t+\tau}{\frac{A^2}{4B}}} - 1) \text{ avec} : A = \frac{2D}{K_s}, B = \frac{2D}{N_1} . N_0$$

$$\tau \frac{x_i^2 + A x_i}{B}$$

L'épaisseur initiale

- Si l'oxydation sèche → x<sub>i</sub>=20 A°

- Si l'oxydation humide  $\rightarrow$   $x_i=0$   $A^{\circ}$

En simplifiant:

1<sup>er</sup> cas: le temps d'oxydation très important

$$\mathbf{t} \gg \boldsymbol{\tau} (\mathbf{x}_0 = \sqrt{Bt})$$

2<sup>eme</sup> cas: le temps d'oxydation très faible

$$(t+\tau) < \frac{A^2}{4B} \implies x_0 = \frac{B}{A}(t+\tau)$$

Dr. CHEBBAH KHEIRA

# 1) Oxydation humide de Si:

| Températur | τ | A    | В           | $\frac{B}{A}$ |

|------------|---|------|-------------|---------------|

| e (°C)     |   | (    | (           | (             |

|            |   | μm)  | $\mu m^2$ ) | <b>μm</b> /   |

|            |   |      |             | <b>h</b> )    |

| 1200       | 0 | 0.05 | 0.720       | 14.40         |

|            |   | 0    |             |               |

| 1100       | 0 | 0.11 | 0.510       | 4.640         |

|            |   | 0    |             |               |

| 1000       | 0 | 0.22 | 0.287       | 1.27          |

|            |   | 6    |             |               |

| 920        | 0 | 0.50 | 0.203       | 0.406         |

|            |   | 0    |             |               |

# 2) Oxydation sèche de Si:

| T    | τ(heures) | A             | В           | $\frac{B}{A}$      |

|------|-----------|---------------|-------------|--------------------|

| (°C) |           | ( <b>μm</b> ) | $(\mu m^2)$ | <br>( μ <b>m</b> / |

|      |           |               |             | <b>h</b> )         |

| 1200 | 0.0019    | 0.040         | 0.045       | 1.12               |

| 1100 | 0.0063    | 0.090         | 0.30        | 0.30               |

| 1000 | 0.029     | 0.165         | 0.0117      | 0.071              |

| 920  | 0.095     | 0.235         | 0.0049      | 0.0208             |

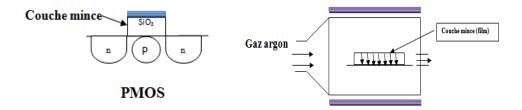

# **Chapitre V : Les couches minces**

# I - Les techniques de dépôt

Les techniques de dépôt qui seront utilisées pour déposer une couche d'isolant ou d'oxyde seront le plus souvent très générales en permettant la réalisation de couches d'autres matériaux tels que des métaux voire des semi-conducteurs.

Plusieurs techniques de dépôt sont possibles industriellement :

- Evaporation thermique.

- Dépôts par pulvérisation cathodique ou canon à électrons.

- Dépôts chimiques en phase vapeur à pression atmosphérique (APCVD).

- Dépôts chimique en phase vapeur assistés plasma (PECVD).

- Dépôts chimiques en phase vapeur à basse pression (LPCVD).

- Dépôts par l'Epitaxie.

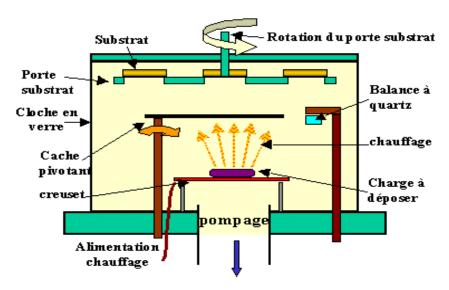

# I-1- Evaporation thermique:

La technique d'évaporation thermique est très simple et consiste simplement à chauffer par effet Joule un matériau qui, vaporisé, va se déposer sur les substrats. La charge du matériau à déposer est placée dans un creuset (en tungstène). Cette technique est applicable notamment pour le dépôt d'aluminium, la température d'évaporation de ce métal étant inférieure à la température de fusion du creuset (en tungstène). Le figure V-1 montre le principe de cette technique ;

**Figure V-1** : Bâti de dépôt par évaporation thermique. Le creuset contenant la charge du matériau à déposer est chauffé par effet Joule

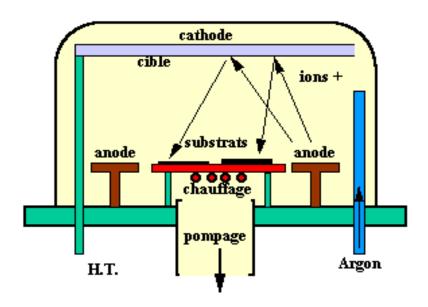

# I-2- Dépôts par pulvérisation cathodique ou canon à électrons :

La pulvérisation cathodique consiste à bombarder une cible par des ions, à arracher les ions de la cible et à les envoyer se déposer sur le substrat. Dans le cas de la figure V-2, montrant de façon simplifié le principe de cette technique, les ions argon, créés par l'excitation haute tension, arrachent de la cible les composés à déposer sur la surface des substrats.

**Figure V-2**: Bâti de dépôt par pulvérisation cathodique. Les ions Argon, créés par l'excitation haute tension, arrachent de la cible les composés à déposer sur la surface des substrats.

# I-3- Dépôts chimiques en phase vapeur à pression atmosphérique (APCVD) :

La technique A.P C.V.D. permettent quant à elles de faire croître des couches d'isolants ou de Silicium polycristallin. Elles s'effectuent en général dans un four dans lequel on introduit les espèces réactants.

Leur avantage elle est donne un bon rendement et bonne uniformité des couches

# I-4- Dépôts chimique en phase vapeur assistés plasma (PECVD) :

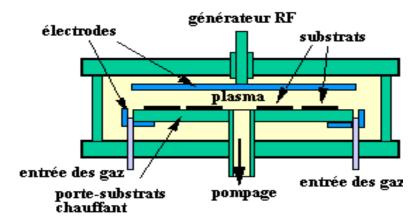

Le dépôt PECVD est donc fondé sur la création d'espèces ou d'éléments à déposer à basse température grâce à l'apport d'énergie sous forme électromagnétique (source radiofréquence en général). Cette technique évite donc des passages à haute température qui peut entraîner une redistribution des dopants par exemple. Industriellement, deux types de four sont proposés, leur schémas de principe étant représentés sur les figures V-3 et V-4:

- four à platine porte-substrat horizontale,

- four à "mur chaud".

Figure V-3: Réacteur plasma à platine porte-substrats horizontale.

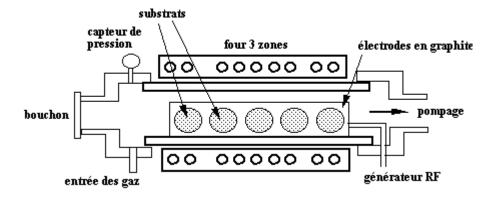

**Figure V-4 :** Schéma d'un réacteur plasma à mur chaud. C'est en réalité un four comportant 3 zones de chauffe dans lequel on réalise un plasma à l'aide de la source radiofréquence.

# I-5- Dépôts chimiques en phase vapeur à basse pression (LPCVD) :

Une autre technique de dépôt comme évoquée ci-dessus est la technique LPCVD. Cette technique consiste à réaliser un dépôt chimique en phase vapeur à basse

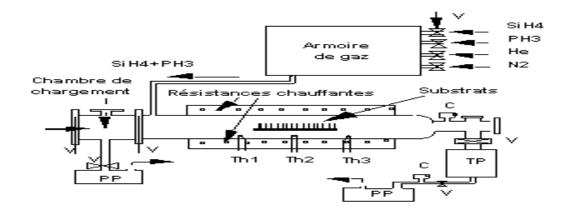

pression. Ce dépôt s'effectue normalement dans un four à mur chaud à des températures de l'ordre de 500 à 600°C. On injecte les gaz qui réagissent et qui synthétisent le matériau à déposer. Dans l'exemple de la figure suivante, le dépôt réalisé est du silicium polycristallin (ou polysilicium) dopé au phosphore. Lorsque le matériau est dopé au cours de son élaboration, on dit qu'il est dopé in-situ.

**Figure V-6** : Réacteur LPCVD pour déposer du polysilicium dopé au phosphore *insitu*.

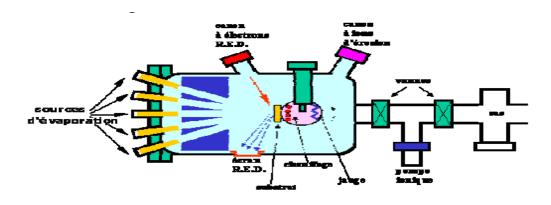

# I-6- Dépôts par l'Epitaxie :

On à plusieurs cibles même principe que la pulvérisation cathodique, Cette technique consiste à envoyer des molécules à la surface d'un substrat dans un vide très poussé afin d'éviter tout choc ou contamination le long du parcours. Le principe consiste à évaporer une source sous vide (cellule de Knudsen) par chauffage (figure V-7). Pour chaque élément à évaporer, il faut adapter la puissance de chauffage des cellules.

Le contrôle des cellules d'évaporation permet de créer un jet de molécules en direction du substrat ; on peut ainsi réaliser couche par couche des structures très complexes telles que les diodes laser et les transistors à forte mobilité d'électron (HEMT). D'où l'obtention d'une très grande précision de croissance, des jonctions très abruptes. Mais cette opération est très lente et ne permet d'utiliser qu'un seul substrat à la fois. La vitesse de croissance est de l'ordre de 1nm par minute. Cette technique est très coûteuse. Toutefois, elle permet un contrôle in situ de la croissance et des épaisseurs des couches.

Figure V-7 : Bâti d'épitaxie par jet moléculaire.

# Chapitre VI : les techniques de la Photolithographie et de gravure

# I) La photolithographie

La photolithogravure consiste à reproduire un masque (physique ou logiciel) sur le substrat.

En général, il s'agit d'obtenir sur un substrat relativement plan des zones spécifiques dictées par le design qui seront recouvertes de résine photosensible afin de protéger ces zones durant certaines étapes de fabrication. En particulier, ce peut être pour protéger les zones recouvrant sur le substrat d'une gravure, d'une implantation ionique ou encore d'un dépôt d'une couche de matériau.

# I-1- Étapes principales :

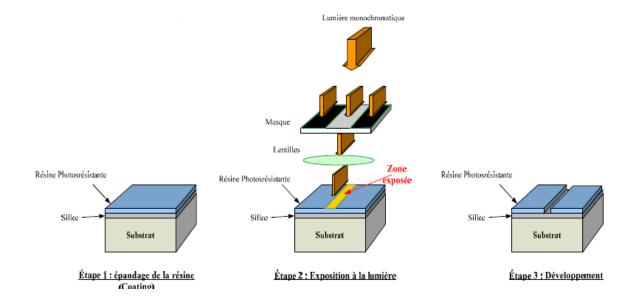

Il y a 3 principales étapes en photolithographie avant de faire le traitement sélectif : Revêtement, Exposition, Développement.

- 1) **Le revêtement** consiste à étaler sur un substrat ou un échantillon une couche de résine (photosensible ou autre) de façon uniforme et contrôlée.

- 2) **L'exposition** consiste à insoler ou exposer la résine photosensible à un rayonnement de lumière ultraviolette de façon sélective en masquant la lumière aux endroits qui n'ont pas à être exposés. Un masque photolithographie est utilisé, lequel est une plaque transparente avec l'image d'un niveau du design réalisé dans une couche opaque aux UV. Après exposition, une image latente correspondant au masque ou à son complément est obtenue dans la couche photosensible.

- 3) Le développement consiste à révéler l'image latente par la dissolution sélective de la couche photosensible. Selon que l'on a utilisé de la résine positive ou négative, l'image obtenue dans la résine sera l'image même du masque ou encore son complément.

**Résine positive :** les zones exposées seront sans résine après développement, le reste qui n'a pas été exposé demeure.

**Résine négative** : les zones exposées demeurent, le reste qui n'a pas été exposé s'en va au développement.

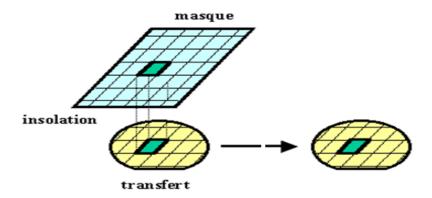

Les figures VI-1 et VI-2 rappellent le principe du procédé de photolithographie ; l'objectif est de transférer un motif (par exemple un rectangle qui correspondra à une zone de source) réalisé sur masque vers une couche de la plaquette.

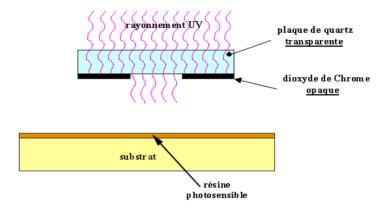

**Figure VI-1**: masque de photolithographie. L'utilisation du quartz est liée à la nature des photons qui sont en général dans le domaine ultraviolet. Le dioxyde de chrome est opaque à ce rayonnement et permet une bonne définition des motifs élémentaires.

**Figure VI-2** : principe de la photolithographie : par insolation, on transfert vers la plaquette le motif défini sur le masque.

**Figure VI-3:**Les étapes de la Photolithographie.

# II- Les techniques de gravure :

Deux techniques sont couramment utilisées :

- la gravure dite par humide, la gravure sèche.

Ces deux types de gravure interviennent de nombreuses fois au cours des procédés modernes. Elles permettent de graver de façon sélective, des couches ou des films afin de créer des motifs (zone actives de dispositifs, grille de transistors, pistes d'interconnexion, etc...). Nous avons vu dans les opérations de photolithogravure qu'en utilisant une résine photosensible on peut protéger des zones. La gravure ne doit donc dans ce cas que concerner les zones non protégées.

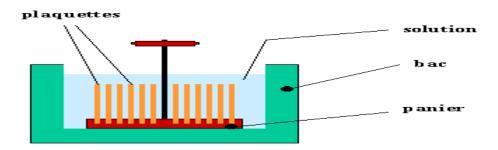

## II-1- La gravure humide:

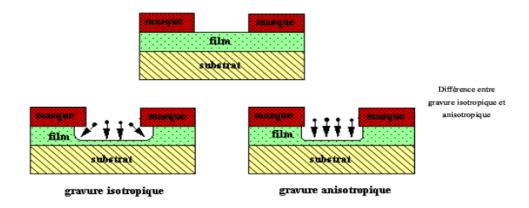

La gravure par voie humide se fait par attaque chimique en solution aqueuse (bain contenant de l'eau). Par exemple, l'oxyde de silicium est gravé par une solution partiellement diluée d'acide fluorhydrique (HF) tamponnée par du fluorure d'ammonium (NH4F). Suivant les concentrations de l'espèce réactante, on étalonne les vitesses de gravure pour un type de couche. En général, par voie humide, la couche est attaquée de façon équivalente suivant toutes les directions de l'espace. On dit que la gravure est **isotropique**.

# Cours de la technologie et fabrication des circuits intégrés

Dans de très nombreuses filières technologiques, la gravure humide est utilisée majoritairement car elle est relativement simple à mettre en oeuvre et que dans des grands bacs, un lot complet pouvant contenir jusqu'à 200 plaquettes peut être traité en une seule opération

Figure VI-4 : Gravure d'un panier de plaquette par voie humide.

L'isotrope de ce type de gravure va ainsi limiter les dimensions des motifs pouvant être réalisés. La gravure humide permet de graver des traits d'une supérieure ou égale à 3 µm, mais elle ne permet pas d'obtenir des dimensions inférieures en raison du phénomène de « surgravure » lié à l'isotropie.la gravure s'effectue en effet dans le sens de la profondeur mais aussi dans le sens de la largeur comme illustré ci-dessous:

Avec un masquage identique, la largeur du motif gravé sera différente selon la méthode de gravure utilisée, isotropique ou anisotropique. Pour les motifs de très petites dimensions, il sera donc préféré une méthode de gravure anisotropique.

#### Avantage:

- Pas ou peu défauts: gravure «douce »

- Bonne sélectivité en fonction composition des matériaux.

- Très bonne sélectivité par rapport au masquage.

#### **Inconvénients:**

- Plutôt isotrope

- Sensible à l'état de surface.

- Contrôle délicat dans le cas des multicouches.

Agitation nécessaire pour l'uniformité de l'attaque sur la surface.

## II-2- La gravure sèche :

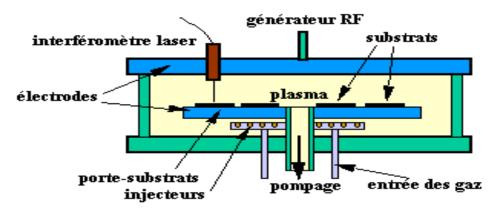

La gravure sèche est en réalité une technique de **gravure plasma** dans laquelle interviennent à la fois les effets de bombardement par des ions et la réaction chimique. On la dénomme R.I.E. (Reactive Ion Etching en anglais).

Le réacteur ressemble au réacteur de dépôt à platine porte-substrats horizontale, mais les gaz injectés sont dans ce cas destinés à graver la couche de surface (figure suivante). De la même façon, on utilise un générateur radiofréquence qui va permettre de générer dans le réacteur les espèces réactives.

Figure VI-5 : Réacteur de gravure plasma à platine porte-substrats horizontale.

Ce réacteur est de conception très similaire à celui de dépôt plasma

Le principe du procédé, représenté figure VI-6, est résumé comme suit :

- génération dans le plasma des espèces pouvant attaquer chimiquement la couche,

- transfert des espèces réactives depuis le plasma vers la surface de la couche à graver,

- adsorption de l'espèce attaquante à la surface,

- réaction avec le matériau de surface. Le matériau produit par la réaction doit être volatile pour pouvoir quitter la surface,

- désorption du produit de réaction,

- diffusion dans l'environnement gazeux.

Si toutes ces conditions sont remplies, on peut alors espérer avoir une bonne gravure plasma. Notons que pour la mise au point de cette étape technologique, la difficulté est de générer des espèces volatiles après réaction en surface.

**Figure VI-6** : Schéma de principe de la réaction de gravure plasma. Pour que la gravure soit efficace, il faut éliminer les produits de réaction.

#### **Avantage:**

- Moins de défauts que l'IBE.

- Vitesse rapide.

## **Inconvénient:**

- Moins anisotrope.

- Bonne reproductibilité: les composantes physiques et chimiques sont indépendantes.

Les principaux gaz utilisés dans les gravures sèches sont indiqués dans le tableau suivant :

| Matériau à | Silicium                         | SnO <sub>2</sub>                 | Siliciures                      | III-V             |

|------------|----------------------------------|----------------------------------|---------------------------------|-------------------|

| gravé      |                                  |                                  |                                 |                   |

|            | SF <sub>6</sub>                  | CHF <sub>3</sub>                 | CFCl <sub>3</sub>               | Cl <sub>2</sub>   |

|            | CF <sub>4</sub> + O <sub>2</sub> | CF <sub>4</sub> + O <sub>2</sub> | CF <sub>2</sub> Cl <sub>2</sub> | SiCl <sub>4</sub> |

|            | HF                               | CF <sub>4</sub> + H <sub>2</sub> | CCl <sub>4</sub>                |                   |

|            | CFCl <sub>3</sub>                | SiCl <sub>4</sub>                | SF <sub>6</sub>                 |                   |

# III- Comparaison des propriétés des gravures humide et plasma :

Dans le tableau suivant les deux types d'étapes sont comparés ; il met en évidence les points forts et les points faibles relatifs.

|                 | Gravure humide | Gravure sèche |

|-----------------|----------------|---------------|

| sélectivité     | Elevée         | Faible        |

| cout            | Faible         | Elevé         |

| durée           | Implorante     | Faible        |

| Technologie     | difficile      | Aisée         |

| submicronique   |                |               |

| anisotrope      | Non            | Oui           |

| Défauts         | Effet galva    | Dommages par  |

| spécifiques     |                | rayonnement   |

| Cout            | Elevée         | Faible        |

| environnement   |                |               |

| Consommation de | Elevée         | Faible        |

| produis         |                |               |

| contrôle        | Difficile      | Assez bon     |

# Chapitre VII : La salle blanche et la salle de montage I-Introduction

Les circuits intégrés sont fabriqués dans un environnement spécifique, qui requièrent des machines élaborées et onéreuses, tant à l'achat, qu'à la maintenance. Un des principaux moyens de lutte consiste à fabriquer ces puces dans un environnement extrêmement contrôlé, on parle de salle blanche car l'environnement doit y être quasiment dépoussiéré afin d'éviter l'introduction de poussière ou d'impureté dans le circuit, lors du process, qui pourrait endommager le fonctionnement de ce dernier.

#### II- Salle blanche

Une salle blanche est une pièce dans laquelle les paramètres ayant une influence directe ou indirecte sur la contamination sont maîtrisés afin de garantir en continu le niveau de qualité de l'air souhaité. D'après la norme ISO 14644-1 (International Standardization Organization, 1999 : La norme ISO 14644 est la norme internationale qui classifie les chambres blanches), la qualité d'une salle blanche est évaluée à partir des concentrations en particule (particules m<sup>-3</sup>) de tailles comprises entre 0,1 µm et 5 µm dans l'atmosphère de la pièce (ISO 1999). D'autres paramètres importants comme la température, l'humidité et la pression sont également contrôlés. La classification ISO 14644-1 des salles blanches et des zones propres est présentée dans le Tableau suivant.

| Classification<br>ISO (N) | Concentration (particules m <sup>-3</sup> d'air) |         |         |            |           |         |

|---------------------------|--------------------------------------------------|---------|---------|------------|-----------|---------|

|                           | θ,1 μm                                           | 0,2 μm  | 0,3 μm  | 0,5 μm     | 1 μm      | 5 μm    |

| ISO Classe 1              | 10                                               | 2       |         |            |           |         |

| ISO Classe 2              | 100                                              | 24      | 10      | 4          | 1         |         |

| ISO Classe 3              | 1 000                                            | 237     | 102     | 35         | 8         |         |

| ISO Classe 4              | 10 000                                           | 2 370   | 1 020   | 352        | 83        |         |

| ISO Classe 5              | 100 000                                          | 23 700  | 10 200  | 3 520      | 832       | 29      |

| ISO Classe 6              | 1 000 000                                        | 237 000 | 102 000 | 35 200     | 8 320     | 293     |

| ISO Classe 7              |                                                  |         |         | 352 000    | 83 200    | 2 930   |

| ISO Classe 8              |                                                  |         |         | 3 520 000  | 832 000   | 29 300  |

| ISO Classe 9              |                                                  |         |         | 35 200 000 | 8 320 000 | 293 000 |

Tableau contient la classification des salles blanches suivant les concentrations maximales (particules m<sup>-3</sup> d'air) pour les particules de tailles comprises entre  $0,1~\mu m$  et  $5~\mu m$  (ISO 1999).

La fabrication de semi-conducteurs nécessite des salles blanches de classe ISO1, soit moins de 10 particules 0,1µm de diamètre par mètre cube.

La qualité de l'air requise est obtenue par un recyclage et un renouvellement partiel de l'air de la salle au travers de filtres spécifiques. Les deux types de filtres utilisés sont les filtres HEPA (High efficiency particulate air) et ULPA (Ultra low penetration air) qui se distinguent l'un de l'autre par leur efficacité de piégeage pour les différentes tailles de particules.

- Les filtres HEPA ont une efficacité de collection comprise entre 99,97 % et 99,997 % pour des particules de taille supérieure à 0,3 μm

- Les filtres ULPA ont une efficacité minimale de 99,9997 % pour les particules supérieures à 0,12 μm.

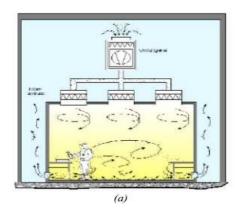

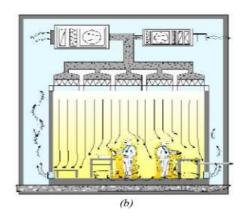

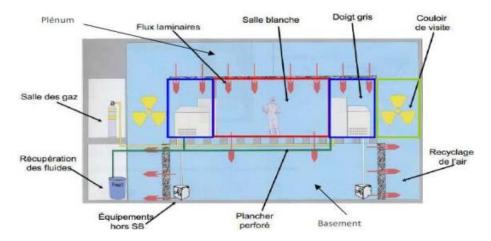

Un flux d'air laminaire traverse verticalement la salle (Figure VII-1). Il est pulsé continuellement à partir du « plenum » qui est une zone dénuée de cloisons. Dans cette zone, l'air recyclé et filtré de la salle blanche est mélangé à un petit complément d'air neuf également filtré, avant d'être uniformément dispersé dans la salle blanche au travers de plafonds ajourés. Il traverse ensuite le sol également ajouré de la salle blanche, avant d'être aspiré par des colonnes placées sur les murs latéraux du local sous salle blanche : le « basement ». Cet air est ensuite traité dans une centrale de traitement d'air et réinjecté dans le plenum (Figure VII-2). Au sein d'une salle propre, le flux d'air peut être turbulent (Figure VII-1-a) - classes ISO 6 à ISO 9 ou unidirectionnel (Figure VII-1-b), appelé historiquement laminaire, classes ISO 5 et inférieures

- a) Flux d'air turbulent : les particules indésirables sont redistribuées dans tout le volume

- b) Flux laminaire : l'air neuf est pulse de manière verticale et "plaque" les particules au sol.

**Figure VII-1 :** Différence entre un flux d'air turbulent et un flux laminaire permettant de contrôler la contamination particulaire en salle blanche

Le système fonctionne en circuit fermé mais il existe une déperdition d'air liée aux aspirations des effluents gazeux des différents équipements. Cet air aspiré est filtré puis rejeté à l'extérieur de l'usine. Il est remplacé par une quantité d'air neuf équivalente afin de respecter un volume d'air stable dans la salle blanche.

Figure VII-2 : Fonctionnement schématique d'une salle blanche.

Rappelons que les principaux vecteurs de contamination sont les personnes, l'environnement ou le milieu (air, surfaces), le matériel (équipements de production, d'exploitation...), les fluides process, les matières premières... Les vêtements des personnels travaillant dans les salles blanches constituent une source potentielle de contamination en particules. Afin de limiter cette source, les expérimentateurs sont revêtus de combinaisons conçues avec des matières n'émettant pas de fibres. De la même façon, les chaussures, les cheveux, les mains, les yeux, la respiration sont des sources de contamination particulaire et chimique. Ces différents éléments ou parties du corps sont donc protégés par des sur-bottes, des cagoules, des gants, des lunettes et des masques (Figure VII-3).

Figure VII-3: Tenue de salle blanche

Outre la contamination particulaire, la salle blanche doit également contrôler la température, l'humidité, et la pression ambiante. Ces paramètres peuvent varier selon l'étape de fabrication mais sont maintenus stables dans un même atelier. L'industrie de la microélectronique est confrontée à trois grands types de contaminants qui sont :

- La contamination particulaire liée aux dépôts de particules sur les wafers ;

- La contamination métallique issue des ions qui se déposent et diffusent dans les plaquettes de silicium ;

- La contamination moléculaire induite par les AMCs (Airborne Molecular Contamination) Suite à la miniaturisation des dispositifs et à l'augmentation de l'intégration des circuits, l'industrie de la microélectronique n'est plus seulement confrontée à des risques de contamination particulaire mais aussi métallique et moléculaire.

Pour limiter ces nouveaux risques, trois mesures préventives ont été mises en œuvre dans les salles blanches (Weineck et al, 2010) : la réduction ou l'élimination de la source de contamination, la ventilation des zones les plus fortement impactées et enfin l'élimination des contaminants moléculaires par filtration chimique.

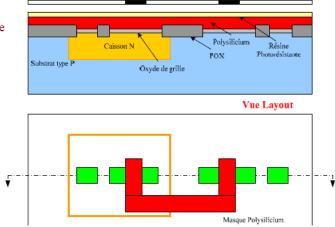

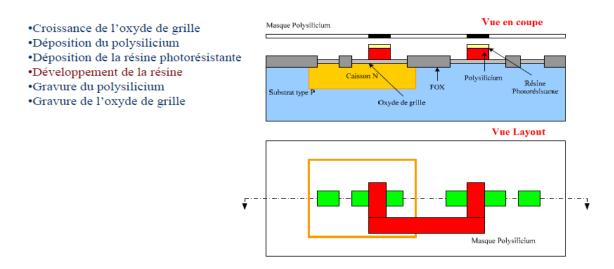

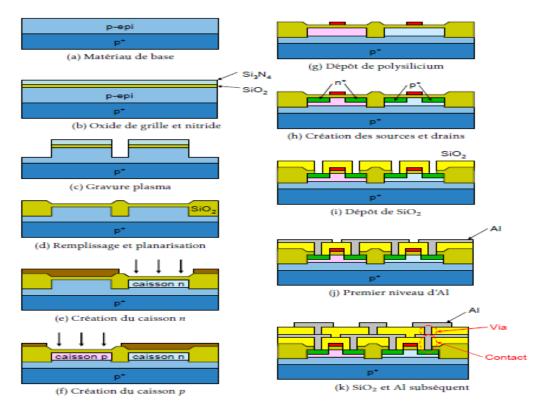

# Chapitre VIII : Exemples de procédés de fabrication I-Procède CMOS simplifie

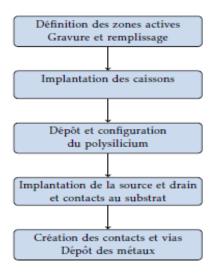

Le procède CMOS simplifie est donne a la figure VIII-1. Le processus commence avec la définition des zones actives : ce sont les régions ou les transistors seront créés. Toutes les autres régions seront couvertes de dioxide de silicium SiO2. Cet oxyde sert à isoler les transistors l'un de l'autre. Des caissons n et p légèrement dop'es sont ensuite crées a l'aide d'implantation d'ions. Pour construire un NMOS dans un caisson p, des zones dopées fortement n sont implantées (la source et le drain). Une mince couche de SiO2 forme la grille du transistor, et cette couche est recouverte de polysilicium. Les PMOS sont formes d'une façon similaire. Par la suite, plusieurs niveaux de fils conducteurs (aluminium ou cuivre) sont déposés pour brancher ensemble les différents transistors.

Figure VIII -1: Etapes du procédé CMOS simplifié.

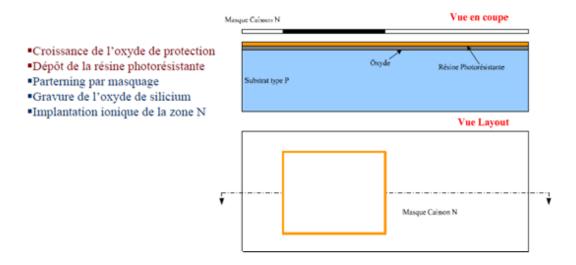

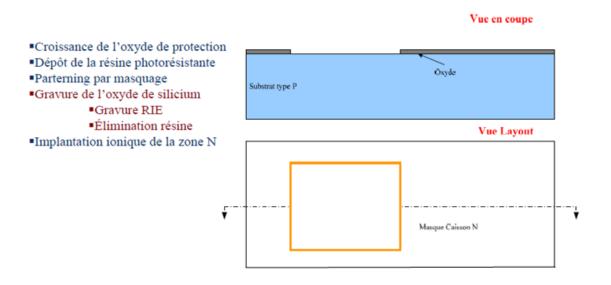

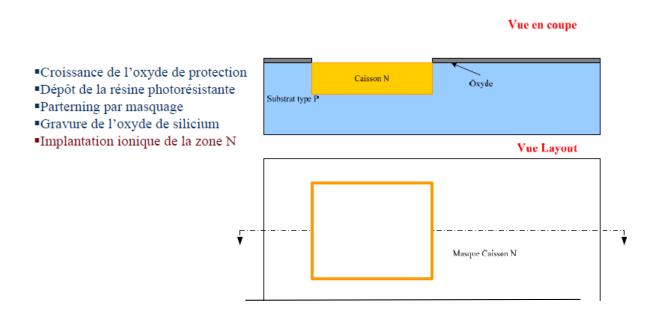

# I-1- Etape 1 : Réalisation du caisson N

La réalisation d'un circuit intégré CMOS démarre à partir d'une tranche de silicium P (substrat), c'est-à-dire d'une tranche de silicium contenant des impuretés constituées d'atomes de bore par exemple. La réalisation des transistors MOS de type P nécessite, au préalable, la réalisation de zones dopées N que l'on nomme *caissons* N. Il est à noter que dans les technologies submicroniques il est d'usage de faire aussi des caissons P pour les transistors de type N (pour améliorer le contrôle du dopage du canal de ces transistors).

La réalisation des caissons N se décompose en cinq sous-étapes dont les trois premières constituent la base de la photolithographie.

# Cours de la technologie et fabrication des circuits intégrés

- Dépôt de la résine photosensible.

- Masquage de cette résine.

- Gravure de l'oxyde de silicium.

- Élimination de la résine.

- Implantation ionique de la zone N et recuit

Figure VIII-2: Réalisation du caisson dopé N.

# a) Masquage de la résine

Les tranches de silicium sont livrées oxydées. Cet oxyde sera gravé par photolithographie pour servir de masque pour l'implantation ionique qui formera les caissons. On commence par déposer une couche de résine photosensible sur la tranche à l'aide d'une tournette. Cette résine sera insolée à travers le masque du caisson N (figure VIII-2).

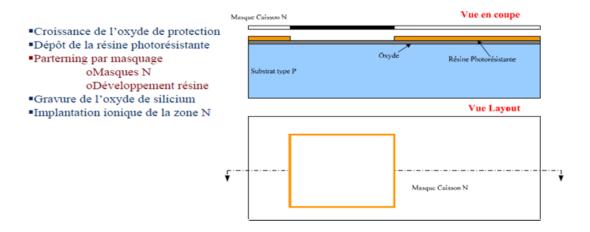

#### b) Développement de la résine

Le développement enlève la résine qui n'a pas été insolée. Seule la zone correspondant au futur caisson N laisse apparaître la silice (figure **VIII-3**).

Figure VIII-3: Réalisation du caisson dopé N.

#### c) Gravure de la silice

La silice est ensuite gravée par attaque chimique ou par plasma (figure VIII-4). On obtient une zone de silicium mis à nu correspondant au caisson N. Le reste de la tranche reste recouvert de silice, donc protégé. La résine est ensuite enlevée par dissolution.

Figure VIII-4: Réalisation du caisson dopé N.

#### d) Implantation ionique de phosphore

Le caisson est maintenant réalisé par implantation ionique de phosphore (figure **VIII-5**). Seule la zone non protégée par la silice est dopée. Cette dernière réalise donc un masque qui défini proprement la zone du caisson N.

Figure VIII-5: Réalisation du caisson dopé N.

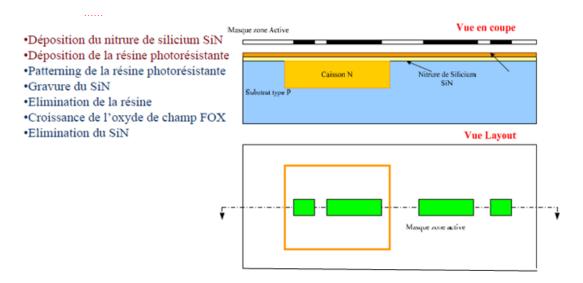

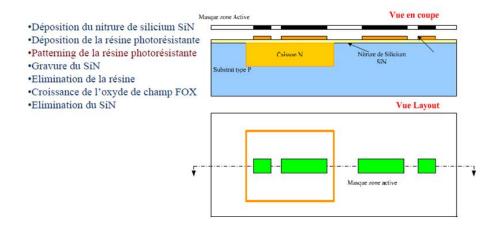

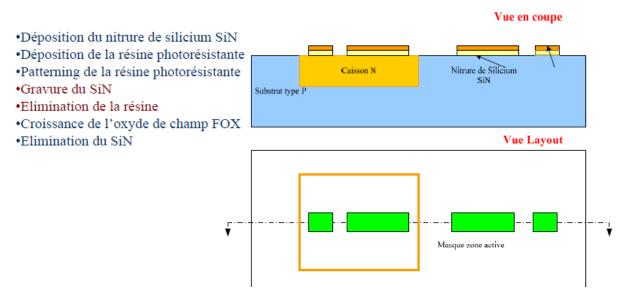

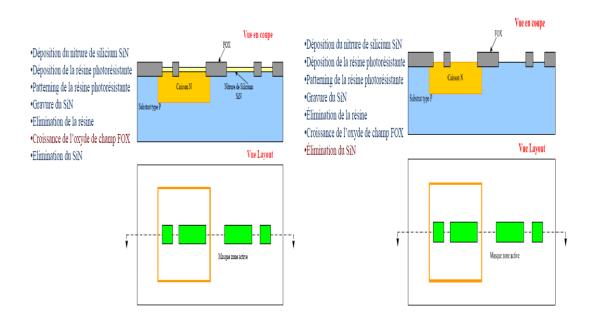

# I-2- Etape 2 : Préparation des zones actives

La seconde étape consiste en la préparation des zones actives, c'est-à-dire des zones qui seront ultérieurement dopées N ou P et qui correspondent aux drains et aux sources des transistors MOS (N et P) ainsi qu'aux contacts des caissons.

La préparation des zones actives se décompose en sept sous-étapes :

- Dépôt de nitrure de silicium (SiN).

- Dépôt de la résine photosensible.

- Masquage et développement de cette résine.

- Gravure du SiN.

- Élimination de la résine.

- Croissance de l'oxyde de champ.

- Élimination du SiN.

Figure VIII-6 : Réalisation des zones actives.

#### a) Dépôt et gravure du nitrure de silicium

La première de ces sous-étapes consiste à réaliser un dépôt par plasma de nitrure de silicium Si3N4. Celui-ci servira de masque pour la future croissance de l'oxyde de champ. La seconde sous-étape consiste à déposer une couche de résine photosensible à l'aide d'une tournette. Cette couche de résine sera ensuite insolée à travers le masque des zones actives puis développée (figure VIII-6). Le nitrure de silicium est ensuite gravé par plasma. Le silicium est mis à nu à l'extérieur des zones qui correspondent aux futures régions actives et aux contacts de caisson. Celles-ci sont recouvertes, donc protégées, par du nitrure de silicium (figure VIII-7).

Figure VIII-7: Réalisation des zones actives.

Figure VIII-8 : Réalisation des zones actives.

# b) Croissance de l'oxyde de champ